Gentian ist eine mesh-fähige kundenspezifische Silizium-Architektur für Transformer-Inferenz.

Der Memory-Wall-Kontext

Transformer-Inferenz ist im Decode speichergebunden. Ein Modell mit 70 Milliarden Parametern und langem Kontext bewegt Hunderte von Gigabytes über externen Speicher für jeden erzeugten Token. Auf GPU-Klasse-Hardware wird der Grossteil der Energie für das Bewegen von Zuständen aufgewendet, nicht für deren Berechnung. High-Bandwidth Memory (HBM) und fortgeschrittenes Packaging (2.5D-Interposer, CoWoS) mildern die Bandbreitenkosten; sie heben die zugrunde liegende Tatsache nicht auf, dass Compute und Speicher getrennte Siliziumkomponenten sind, verbunden durch einen Link, der pro Byte eine Grössenordnung mehr kostet als ein On-Die-Zugriff.

Eine verteilte Inferenz-Architektur, die Parameter und Aktivierungen dort hält, wo die Berechnung stattfindet — anstatt sie über eine Speichergrenze zu schicken — tauscht ein externes Bandbreitenproblem gegen ein internes Koordinationsproblem.

Die Architektur

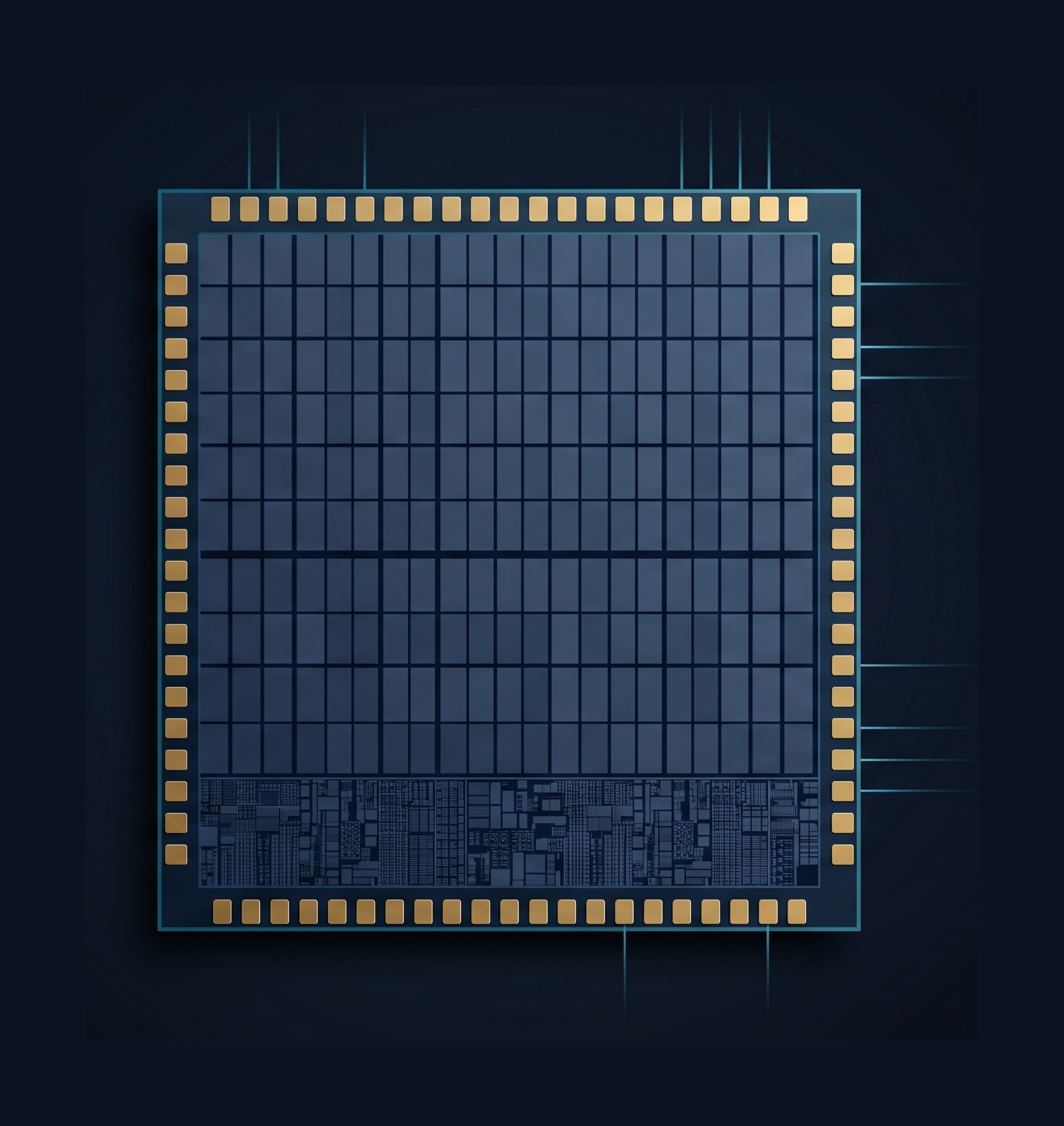

Gentian ist ein Tile-Mesh, in dem jeder Tile seinen Anteil des Modellzustands im On-Die-SRAM hält und Tiles über ein reguläres Mesh über Die-Grenzen hinweg auf einer Standard-Leiterplatte komponieren. Das Design verpflichtet sich auf vier Engineering-Invarianten:

- Reguläre Mesh-Topologie. Nur Nachbar-Links; keine Crossbar, kein globaler Bus.

- Master-freie Peer-to-Peer-Koordination. Kein zentraler Scheduler oder Arbitrator.

- Stationäre Daten. Gewichte und Aktivierungen bleiben auf ihrem Tile; nur kleine Traversal-Objekte bewegen sich.

- Clock-Velocity-Interconnect. Inter-Die-Hops auf CPU-Takt, nicht über paketierte SerDes-Protokolle.

Zusammen bringen die vier Commitments die Wall-Clock-Laufzeit auf die kausale untere Schranke paralleler Berechnung und machen die Architektur node-agnostisch und portierbar über gängige advanced-node Prozesse.

Projektstand

| Meilenstein | Status |

|---|---|

| Ende-zu-Ende-Ausführung | Ein echter trainierter Transformer läuft auf dem Mesh |

| RTL | gegen C++-Referenz validiert |

| Physical Design | Place-and-Route-Signoff erreicht |

| Architektur-Paper | Preprint in Vorbereitung |

| Simulationsarchiv | Partnern unter NDA zugänglich |

| Tape-out auf kommerziellem Node | Foundry-Partner-Auswahl läuft |

Zusammenarbeit

Technisches Briefing, Architektur-Manuskript, PnR-Reports und Simulationsarchiv werden unter gegenseitigem NDA bereitgestellt. Ein Partnergespräch geht direkt in die Engineering-Review-Phase über. Breiterer Forschungskontext unter cybiont-Forschung.